In a collaborative effort, Taiwan Semiconductor Manufacturing Company (TSMC) and Taiwan’s Industrial Technology Research Institute (ITRI) have unveiled their jointly developed SOT-MRAM memory. The new memory device, designed for in-memory computation as well as upper-level cache usage, outperforms DRAM and retains data even after power is switched off. It seeks to replace STT-MRAM memory, using 100 times less energy during operation.

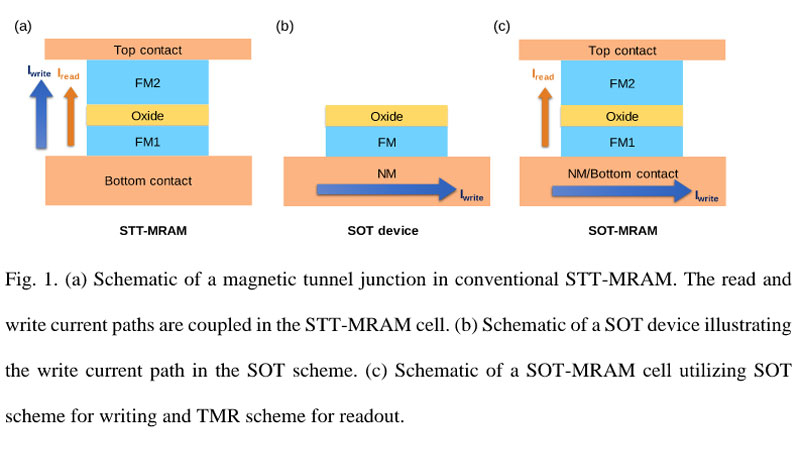

For a considerable time, Spin-Transfer Torque Magnetic Random Access Memory (STT-MRAM) had been a promising candidate for non-volatile memory and high-level cache memory. The power consumption of STT-MRAM was significantly lower than conventional MRAM as it transferred magnetization to the storage cell through a tunnel junction using spin-polarized current.

The development of SOT-MRAM pushes these boundaries further. Cell magnetization occurs through the spin-orbit torque, which combines two phenomena: the spin Hall effect and Rashba-Edelstein effect. The net result is that an induced magnetic field from the conductor’s spin current influences the adjacent ferromagnet, reducing the energy requirements of SOT-MRAM.

Other salient features of SOT-MRAM include separate write and read circuits for improved performance and enhanced wear resistance.

“This elementary cell delivers both low energy consumption and high-speed operation with speeds up to 10 ns, says Dr Shi-Chi Chang, General Director of Electronic and Optoelectronic System Research Laboratories at ITRI. The overall computational performance can be further enhanced with the implementation of in-memory computing techniques. Looking ahead, this technology has the potential for uses in high-performance computing (HPC), artificial intelligence (AI), automotive chips and beyond.”

With timings at 10 ns, SOT-MRAM comes closer to SRAM (delays up to 2 ns) than ordinary DRAM memory (delays up to 100 ns and above) and is way faster than today’s popular 3D NAND TLC, with delays between 50 and 100 µs. However, SOT-MRAM will not appear in processors and memory controllers anytime soon, just as STT-MRAM, which has been under development for over 20 years, has not been highly sought after. While these are future developments not expected soon, they are nonetheless necessary for effective in-memory computing and autonomous power devices.